# SURVIVING AND THRIVING IN A MULTI-CORE WORLD

# AN EBOOK FROM AMD DEVELOPER CENTRAL

November 2006

# Trademarks

© 2005-2006 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, AMD Athlon, and AMD Opteron and combinations thereof are trademarks of Advanced Micro Devices, Inc. Materials marked with JupiterMedia copyright are used by permission of JupiterMedia HyperTransport is a licensed trademark of the HyperTransport Technology Consortium. Microsoft and Windows registered trademarks of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **Table of Contents**

| Driving in the Fast Lane: Multi-Core Computing for Programmers, Part 1                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Learn how applications and operating systems behave on multi-core systems 5                                                                            |

| Driving in the Fast Lane: Multi-Core Computing for Programmers, Part 27                                                                                |

| Learn how to leverage the capabilities of multiple cores to create more efficient applications. It's all about threading – multiple threading, that is |

| Multiple Threads, Multiple Cores, Multiple Gains: Part 1 12                                                                                            |

| Learn how to evaluate the benefits of preemptive multitasking and the opportunities for utilizing it                                                   |

| Multiple Threads, Multiple Cores, Multiple Gains: Part 2                                                                                               |

| Learn how to use multiple cores for faster performance                                                                                                 |

| A Quick Look at the Benefits of Multi-Core Computing                                                                                                   |

| Learn how AMD Direct Connect Architecture and AMD HyperTransport technology can help you improve your multi-tasking19                                  |

| Learn how threading and virtualization can work together to make your application fly                                                                  |

| Living in a Multi-Core World: Tips for Developers                                                                                                      |

| Learn how to best take advantage of advances in multi-core processing                                                                                  |

| Implicit Threading, Explicit Threading: What's Best, How to Choose                                                                                     |

| Learn how to use OpenMP for simple, portable means of threading code and maximizing performance on multiple cores                                      |

| Coarse-Grained Vs. Fine-Grained Threading for Native Applications, Part 1                                                                              |

| Learn when to choose coarse-grained threading for your application                                                                                     |

| Coarse-Grained Vs. Fine-Grained Threading for Native Applications, Part 2                                                                              |

| Learn when to choose fine-grained threading for your application                                                                                       |

| Optimizing for Multi-Core with AMD CodeAnalyst                                                                                                         |

| Learn how to use CodeAnalyst to optimize application performance                                                                                       |

| Taking Advantage of Concurrent Programming for Windows, Part 1:                                                                                        |

| Learn the simplest multi-core parallelism that works                                                                                                   |

| Taking Advantage of Concurrent Programming for Windows, Part 2                                                                                         |

| Learn coding techniques for multiple cores61                                                                                                           |

| Taking Advantage of Concurrent Programming for Windows, Part 3                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Learn how to prevent "premature optimization" with data caches                                                                                                                                    |

| Taking Advantage of Concurrent Programming for Windows, Part 4                                                                                                                                    |

| Learn how concurrent programming can affect performance                                                                                                                                           |

| Linux on Multi-Core: Why WAS CE Should Get Your Attention79                                                                                                                                       |

| Learn about the Websphere Open Source Appliance with Opteron inside                                                                                                                               |

| Making Multi-Cores Count: An ISV Licensing Primer                                                                                                                                                 |

| <i>Learn how ISV license models can support multi-core processing and virtualization.</i><br>                                                                                                     |

|                                                                                                                                                                                                   |

| White Paper: Device Driver & BIOS Development for AMD Systems                                                                                                                                     |

| White Paper: Device Driver & BIOS Development for AMD Systems       87         Introduction       89                                                                                              |

|                                                                                                                                                                                                   |

| Introduction                                                                                                                                                                                      |

| Introduction                                                                                                                                                                                      |

| Introduction                                                                                                                                                                                      |

| Introduction                                                                                                                                                                                      |

| Introduction89Multiprocessor Development Challenges90Simultaneous Thread Execution90Synchronizing Access, Enforcing Run Order92PCI Bus Device Development Notes93                                 |

| Introduction89Multiprocessor Development Challenges90Simultaneous Thread Execution90Synchronizing Access, Enforcing Run Order92PCI Bus Device Development Notes93BIOS Notes for Multiprocessing94 |

## Driving in the Fast Lane: Multi-Core Computing for Programmers, Part 1

Learn how applications and operating systems behave on multi-core systems.

### by Alan Zeichick

The main road near my house, called Skyline Drive, drives me nuts. For several miles, it's a quasi-limited access highway. But for some inexplicable reason, it keeps alternating between one and two lanes in each direction. In the two-lane part, traffic moves along swiftly, even during rush hour. In the one-lane part, the traffic merges back together, and everything crawls to a standstill. When the next two-lane part appears, things speed up again.

Two lanes are better than one—and not just because they can accommodate twice as many cars. What makes the two-lane section better is that people can overtake. In the one-lane portion (which has a double-yellow line, so there's no passing), traffic is limited to the slowest truck's speed, or to little-old-man-peering-over-the-steering-wheel-of-his-Dodge-Dart speed. Wake me when we get there. But in the two-lane section, the traffic can sort itself out. Trucks move to the right, cars pass on the left. Police and other priority traffic weave in and out, using both lanes depending on which has more capacity at any particular moment. Delivery services with a convoy of trucks will exploit both lanes to improve throughput. The entire system becomes more efficient, and net flow of cars through those two-lane sections is considerably higher.

Okay, you've figured out that this is all about dual-core and multi-core computing, where cars are analogous to application threads, and the lanes are analogous to processor cores.

I'll have to admit that my analogy is somewhat simplistic, and purists will say that it's flawed, because an operating system has more flexibility to schedule tasks in a single-core environment under a preemptive multiprocessing environment. But that flexibility comes at a cost. Yes, if I were really modeling a microprocessor using Skyline Drive, cars would be able to pass each other in the single-lane section, but only if the car in front were to pull over and stop.

### No, Cores Aren't Really Cars

Okay, enough about cars. Let's talk about dual-core and multi-core systems, why businesses are interested in buying them, and what implications all that should have for software developers like us.

A core is the part of a microprocessor that does all the computing. It comprises a central processing unit (the thing that executes the instruction set), as well as the L1 and L2 instruction and data caches. In a typical single-core Opteron processor's silicon, you have one core, as well as a memory controller and HyperTransport bus interfaces. The core is only able to handle one task at a time.

In a multi-core chip, you have multiple cores—the central processing unit and L1/L2 caches—on that piece of silicon. Each core can process one task at a time. However, you still only have one integrated memory controller and one set of HyperTransport bus interfaces. Connecting them all together is a crossbar switch, which gives each core equal access to the memory controllers and I/O subsystem.

The benefit of a multi-core system is that the microprocessor can handle multiple threads simultaneously, and those threads can be completely independent. In that sense, it's like northbound Skyline Drive, which can handle multiple lanes of traffic. Thanks to the crossbar switch and integrated memory controller, each core can access other system resources without disturbing what's going on in the other core (as if traffic in the left-hand lane can make a right turn without first moving into the right-hand lane).

It's best to consider a dual-core processor as an upgrade for a single-core processor, because you get twice as many threads being processed. A single-processor system with a dual-core chip can handle two hardware threads—just like a dual-processor single-core chip. Also, the efficient design of the internal crossbar switch in AMD's Opteron design means that if two threads need to talk to each other, they can do so inside the silicon, therefore data can be exchanged very rapidly. This works today in single-processor dual-core systems; within a few years, AMD says it will be able to do this within multi-processor systems as well. (By contrast, the Northbridge design used by Intel's dual-core Xeon processors means that the cores within the silicon can't talk to each other directly; they have to talk using the slower external front-side bus.)

You probably shouldn't think of a dual-core processor as a replacement for two single-core processors. In other words, it's not a good idea to replace a four-processor, single-core server with a dual-processor, dual-core server. While it might seem that you'd have the same performance—after all, you would have as many cores (four), that's not the case—there are two drawbacks.

First, in order to reduce power consumption and cooling, each of the cores running inside a dualcore processor is clocked slightly slower than an equivalent single-core Opteron processor. Thus, today you can have a piece of silicon that's a 2.6GHz single-core Opteron chip, or a 2.2GHz dualcore chip. It's likely that the dual-core chips will always be clocked slower than single-core; when quad-core chips come out, they'll be clocked slower still. (To use my car analogy, the dual-lane road has a lower speed limit than the single-lane road, in order to reduce net auto emissions on that stretch of highway.)

The other drawback exists because there's only a single shared memory controller, and a single set of shared HyperTransport interfaces—two cores running flat-out will have less memory and I/O bandwidth (to continue the car analogy: on a multi-lane highway, on-ramps and off-ramps are single-lane roads.) Most of the time, there's ample I/O bandwidth, so this isn't a bottleneck—but it's still something to consider.

The upshot of all this is that "conventional wisdom" says that the fastest dual-core processor won't actually run twice as fast as the fastest single core chip; in the real world, it'll produce a speed improvement of about 1.5 to 1.7 times the performance, depending on the application's I/O requirements. Again, that's why you should think of a dual-core chip as an upgrade for a single-core chip, not as a replacement for two single-core chips.

### What This Means for Developers

In our car world, imagine a lot of the traffic on Skyline Drive was municipal: police and fire trucks, trash trucks, and street sweepers. That's the case on a typical PC or server: The operating system produces a huge number of threads. A modern operating system, like Linux, 32-bit or 64-bit Windows, or Solaris is inherently multithreaded: A process, such as the network listener, print spooler, or keyboard monitor, is broken up into small chunks. In a multi-processor or multi-core

system, the OS's thread scheduler dynamically puts them into the correct lane for most efficient processing.

Unfortunately, many applications, particularly those written for desktop or notebook PCs, aren't written with threading in mind. This is particularly problematic on desktops, where each application is designed to run in the foreground, and doesn't "play well with others." Take a typical desktop app: The entire application runs in a single thread. While the OS's thread scheduler will put it onto any available processor, the entire application is a convoy that doesn't know how to change lanes, so while other cars are zipping all around it, the whole chain is constrained by the performance of its slowest components, like its I/O functions. So, if one driver has to stop for gas or hits a red light (i.e., is stuck in a wait state), the entire convoy has to stop.

In this case, however, the problem isn't that the thread is stuck behind some other application (the operating system will use thread scheduling to solve that problem). It's that in a single-threaded application, performance is constrained by the least-efficient part of that application itself. So while the app is reading data from the relatively slow disk drive, other meaningful processing within that app comes to a halt. While the Linux or Windows user- interface handlers do a good job of masking this, because they'll keep the mouse moving and so on, a single-threaded application can't do more than one thing at a time unless it's written to use threads.

Historically, of course, desktops and PCs could only process one thread at a time (i.e., they were on single lane highways), so the benefits of writing multi-threaded applications were minimal. But today, when it's clear that in a few years, most consumer and business desktops will be multi-core machines, it's time to begin finding the bottlenecks in those single-threaded apps, and rewriting them to handle threading. New applications should also be designed, right from the outset, to use threading.

### Next Time: More Silliness?

In Part II, we'll dive into the issues of developing threaded applications. We'll discuss task-level parallelism, the implications of threading on compiled and managed languages, and introduce concepts like implicit parallelization and explicit parallelization of code using OpenMP. We'll conclude by talking about threading tools, and why you'll need them for analyzing and debugging multithreaded applications.

© Copyright 2006 Jupitermedia Corporation. All Rights Reserved.

# Driving in the Fast Lane: Multi-Core Computing for Programmers, Part 2

Learn how to leverage the capabilities of multiple cores to create more efficient applications. It's all about threading – multiple threading, that is.

### by Alan Zeichick

Take a look at your computer. If you're running Linux or Solaris, check the list of processes, if you're using Windows, view the Task Manager. Your workstation is likely running dozens of processes. Many (or most) of those are owned by the operating system; today's modern operating systems are all extensively multithreaded. Some of those processes involve background tasks that are waiting, without consuming many CPU cycles most of the time. On my Windows desktop, there's an iPod service application, Norton AntiVirus, the Acrobat tray icon, and quite a few schedulers. There are also active applications, such as Word (currently in the foreground), AOL Instant Messenger (currently dormant), iTunes (playing "The Chain," by Fleetwood Mac), and Eudora, among others. There are also the core tasks that keep Windows alive—the network listener, UI handlers, and some device drivers.

A core part of any operating system is its task or process scheduler, which decides which threads and processes get access to a core, and how long they can stay there. Applications that spawn multiple threads, like Eudora, Word, and Outlook, provide the operating system more to work with. If Eudora or Outlook uses one thread to handle the user interface and another to communicate with the network, the OS helps it be more responsive to the user, and a better citizen when it comes to sharing resources.

Because modern operating systems are extensively multi-threaded, they automatically benefit any time you install them onto a multi-cored environment, where each core can take full advantage of system resources, each has its own caches, and each can directly access its own cache, main memory, and I/O.

In my particular case, my everyday workstation uses two single-core processors, but the effect is the same as if I had a single dual-core CPU. Windows XP automatically schedules tasks to run on both cores. Therefore, even if I don't do a thing with my applications--and even if my applications are not written to use threads at all—I benefit from having multiple cores at my disposal, because more threads can execute at one time, and the OS has more flexibility to maximize resource utilization.

For example, the operating system can keep a UI thread active and current even while a disk I/O thread is running, so that the UI doesn't have to halt momentarily while the OS preemptively swaps it out to service the disk I/O thread. Figure 1 shows the types of thread resources my dual-processor system is using at this particular moment.

**Figure 1.** While Alan is writing this article, his dual-processor Opteron workstation is keeping both processors busy with 610 threads in 54 separate processes.

### More Than the OS

If the only multithreaded software on your system consists of the operating system, you'll definitely benefit—the OS spins out hundreds of threads. However, you're leaving performance on the table, not to mention user.

Take Outlook. If it were a single-threaded application, it wouldn't let you write new messages while it was sending/receiving messages from the server. But because it's a well-threaded application, it can do both tasks. On a single-core system, the OS handles task scheduling, giving both the UI and send/receive threads some attention, but neither can run at the same time. In a multi-core system, the scheduler can let both run at the same time—or if network conditions slow, it can put a wait on the send/receive threads without affecting the UI threads at all. The result is an application that's more effective and more satisfying.

Many modern commercial applications (but not all of them) are written to use multiple threads. Sometimes that threading is explicitly designed into the app, like it was with Outlook. Sometimes the threads appear because the optimizing compiler implicitly threaded some parts of the application during the build process. That's great for commercial software, but the challenge is to bring that same level of threading into your own applications, whether they're being written for customers/commercial sale, or for in-house usage. That will not only make the applications better to use (think about the jerky editor on a single-threaded e-mail app), but also better able to exploit the performance of multi-core desktop and notebook PCs.

**Note:** Everything in this article applies equally well to server applications, but I'm going to focus on desktops/notebooks because enterprise server software developers have been creating threaded applications for many years. Because the only multi-cored PCs were rare dual-processor workstations and gamer systems, mainstream desktop app developers have had fewer reasons to explore threading. Because of this, but also because desktop users are more sensitive to the perceived performance of foreground tasks, the introduction of dual-core chips presents a more significant paradigm shift for desktop developers than it is for server app developers.

### Three Approaches to Threading

When you look at threading applications, there are three ways to go, and they greatly depend on two separate questions: First, are you building from scratch or trying to retrofit an existing

application? Second, are you going to be compiling native code or are you writing for a managed runtime environment, such as .NET or Java? Depending on those answers, you can look at task-level parallelism, compiler-driven parallelism, or managed parallelism.

**Task-Level Parallelism.** If you're writing a new application, you have the opportunity to design the application in order to parallelize at the task layer. That's the best way to go; you can see that in applications like Outlook or Eudora, which are architected in a way that logically separates different tasks into different threads, and which use semaphores and other mechanisms to enable communication between those threads.

I'll be honest: Writing an application to exploit *task-level parallelism* can be difficult at first; it's like making the transition from structured to object-oriented programming. Think carefully about the best ways to split the code. Some obvious places are areas that have distinctly different needs. For example, a UI layer is I/O bound, but handwriting recognition is CPU-bound. In an application that uses network databases, one thread can communicate and sync with the network and fill a local cache, while another thread works out of that cache.

For another example, a game application might use task-level parallelism to separate out the game physics, the audio, the graphics, the strategy, and the different artificial intelligence characters in the game. If the game runs over a LAN, the related housekeeping and communication over the network could be two separate tasks.

The beauty of task-level parallelism is that it's independent of the underlying technology—it works well on both compiled and managed applications, and doesn't require special compilers. The downside is that it's difficult to retrofit a new design to existing applications, unless they're already written in a manner that happens to be sufficiently modular.

**Compiler-Driven Parallelism.** Independently of whether or not you implement task-level parallelism, you can—and should—enlist your compiler to help parallelize your native code.

Some optimizing compilers for C/C++ and Fortran can implicitly parallelize code by analyzing chunks of application logic. A typical optimization would be to split a loop into several pieces, each of which can be run in its own thread. For example, say you have a loop that iterates 1000 times in order to perform some operation on elements of a data structure, and that it's not important that those operations be performed sequentially. The compiler might split it into two separate threads, one with a loop that initializes elements 0-499, the other which takes care of elements 500-999. Clearly, there must not be loop-carried data dependencies that might cause the parallelization to mess up the results. If the compiler's not sure, it'll leave it alone.

Refer to your compiler's documentation to see what levels of implicit parallelization it offers. You'll generally need to invoke such parallelization through the use of switches. The best news about implicit parallelization is that it requires no source code changes.

A more powerful technique is to use *explicit parallelization*, such as through the use of OpenMP directive. OpenMP [http://www.openmp.org/] is an industry standard that allows you to easily indicate, inside the source code, which bits of code can and should be split off into different threads.

If you then compile using the appropriate switches, the compiler will dutifully generate the multithreaded code, taking care of all the necessary plumbing. If you don't specify the OpenMP compiler switches, the compiler ignores those directives, and generates single-threaded code. This lets you compile both ways, then perform regression tests and benchmarks to see if there were any unwanted effects from the parallelization.

This is another case when I'm going to say, "Refer to your compiler documentation for more information." Future articles on the AMD64 DevSource will discuss programming with OpenMP.

**Managed Parallelism.** Implicit parallelism, and explicit parallelism using OpenMP, are wonderful for adding threads to compiled code. But what about *managed* code for Java or .NET? The good news is that the Java Runtime Environment and the Common Language Runtime mask a lot of the details of application execution and optimization. The bad news is that, for the most part, there's not much you can do to drive increased threading. So, your best bet is to focus on task-level parallelization, and don't worry about using threads to improve the performance of individual tasks.

With that said, you can help improve the threading of specific tasks, but you'll have to handle all the plumbing yourself.

If you're coding in Java, use the Java Thread API to instantiate an object of type Thread and then send it a start() message to spin it off into its own thread. A good tutorial on this is on the IBM developerWorks site; see http://www-128.ibm.com/developerworks/library/j-thread.html.

What about .NET? Microsoft has provided a great deal of documentation on threading managed applications. See the.NET Developer's Guide [http://msdn.microsoft.com/library/default.asp?url=/library/en-us/cpguide/html/cpconmanagedthreadingbasics.asp] for details.

### You'll Also Need Tools

Let's say you've gone through all the steps above—you've implemented task-level parallelism, leveraged implicit and explicit threading with the C++ or Fortran compiler or using the threading facilities in Java and .NET. Now... How efficient is your threaded code? That's a good question. How about debugging threads? That's another good question. The answers typically require specialized tools.

A future article here on the AMD64 DevSource is going to look more deeply at the specialized threading tools, but I'll point you to one of them, the AMD **CodeAnalyst Performance Analyzer**. This is a neat tool for both 32-bit and 64-bit Linux and Windows—and it's free.

The Windows version provides a wide range of analysis, including system-wide profiling and thread utilization for both compiled and .NET applications. The Linux version, for the Red Hat and SUSE 2.4 or 2.6 kernel, can handle both native and Java applications.

And now if you'll excuse me, it's time to find some new music; iTunes has finished its Fleetwood Mac run. I think the appropriate next song for thinking about dual-core processors might be by Phil Collins: Anyone for "Two Hearts"?

© Copyright 2006 Jupitermedia Corporation. All Rights Reserved.

## Multiple Threads, Multiple Cores, Multiple Gains: Part 1

Learn how to evaluate the benefits of preemptive multitasking and the opportunities for utilizing it.

#### by Peter Aitken

When I used to work at a major university, my colleagues would sometimes complement me on my ability to multitask. I could spend a few minutes on the phone, then return immediately to writing an article, then stop doing that to talk to a student for a while, then read my mail, and so on. I suppose this was a useful skill, but that fact is that it was *not* multitasking—I was never actually doing more than one thing at the same time. Rather, what I was doing was more accurately called task switching, moving quickly and without interruption from one task to another. At the time I was unaware that my behavior modeled what goes on in just about every desktop computer.

We've all sat at our computer and seen two or more things going on at the same time. Who hasn't worked on a spreadsheet while another document is being printed and a large file is downloading from the Web? This sure seems like multitasking, but the fact is that the vast majority of computers can't multitask (in the strict sense of the word), all they can do is task switch—just like me.

While a central processing unit, or CPU—the "brains" of a computer—can do only one thing at a time, it can do things very quickly indeed. Modern operating systems such as Windows and the Mac OS have taken advantage of this fact to implement a form of task switching that is called *preemptive multitasking*. Let's see how this works.

Suppose that three programs are active—it doesn't matter what they are or what they are doing, we'll just call them A, B, and C. The OS lets program A use the CPU for some period of time, perhaps 10 milliseconds (the actual duration of the "time slots" depends on the CPU and OS in use). At the end of the time period the OS saves all the information about what A was doing and turns the CPU over to program B. After another 10 milliseconds, program C gets its 10 milliseconds, and then it's back to A again. Each time there is a task switch, the information about the task that's pausing is saved and the information about the task that is resuming is restored.

Because human perceptions are a lot slower than the CPU, and because most peripheral devices such as printers and networks are also slower, there's no perception on the user's part that anything has paused. Even if a program has only 10% of the CPU time, that is plenty to take care of the fastest typist and the speediest printer. What we see is a computer that is happily doing 2, 3, or more things at the same time. While the term multitasking may not be precisely correct for what a one-CPU computer does, the term is used in that way by most people and I shall do so also.

### **Preemptive Multitasking and Priorities**

I mentioned that Windows supports preemptive multitasking. *Preemptive* means simply that the OS is in charge of what programs get CPU time, how much time they get, and when they get it. In other words, the OS can preempt a program in order to let another run. This is in contrast to *cooperative multitasking* where the programs themselves voluntarily relinquish the CPU after having executed for some period. Cooperative multitasking was used by the Windows OS prior to Windows 95 and Windows NT, and by the Macintosh prior to OS X. Cooperative multitasking makes OS design much simpler because the OS does not have to monitor and control program

use of the CPU, but it is less stable because a single badly written application can hog the CPU.

You might think that different programs would have different levels of need for the CPU—and you would be 100 percent correct. Windows defines four levels of priority:

- Real time used for tasks that cannot be interrupted, such as streaming video and games with complex graphics.

- High used for time-critical tasks that need to execute essentially immediately to function properly, such as the Windows Task manager.

- Normal used for tasks that have no special CPU scheduling demands. Most application programs, such as a word processor or e-mail client, use this priority.

- Idle used for processes that should run only when no higher priority process is active, in other words when the system is idle. A background backup or file indexing app would fall into this category.

Priorities are assigned by the OS. A program can request a particular priority and generally speaking will get it, but the OS has the final say.

### Multithreading

You have probably heard the term *multithreading*. What is this, and how does it relate to multitasking? First, let's go over some terminology. A program running on a computer is technically known as a process. Each process has its own memory context—a region of the system's RAM that it and only it has access to. The OS prevents any process from meddling with memory that does not belong to it. The reason for this is probably obvious—if one program could alter memory belonging to another program, or to the OS itself, it is a recipe for disaster!

A *thread* is the basic unit to which the OS assigns processor time. By default, each program—that is, each process—has a single thread. As the OS gives each program its slot of CPU time it is actually assigning time to the process's thread.

Now we can understand multithreading. It refers to the case when a single process has more than one thread. Most programming languages provide developers with the tools to create and use additional threads in a process. When a process has more than one thread, all of the threads have access to the process's memory context. This makes it easy for threads to exchange data, but it also opens the door to potential problems that I'll discuss soon.

### Multithreading Benefits

What's important to realize are the consequences of a process having two or more threads:

- Each thread will be allocated its own share of CPU time so the program as a whole can get more time than if it had just one thread.

- One busy thread—for example, one that is performing a long numerical calculation—will not prevent other parts of the program (that are on other threads) from running.

You might think that the first of these factors would result in a multithreaded program running faster. Generally speaking, however, that is not the case, at least not on single CPU systems. With multi-processor systems, as exemplified by AMD's multi-core designs, true performance gains are possible. Sometimes very significant performance gains can be had from multiple threads—more on this in the next article.

It's the second factor that motivates most use of multithreading in today's applications. If the program has to perform a CPU-intensive task, such as a long mathematical calculation, sorting a large amount of data, or loading a large file from disk, that task can fully occupy a non-multithreaded program's only thread.

And guess what? That lone thread is also responsible for responding to mouse and keyboard input and updating the display. The result is that while the time-consuming task is executing, the program "freezes" and does not respond to user input or update the display. This is a sure way to annoy your users, and most programmers know to put such time-consuming tasks on their own thread, leaving the program's default thread free to respond to user input.

### What's Next?

Systems with more than one processor open the door to true multitasking, with two or more tasks running literally at the same time. Such true multitasking environments also enable multithreaded programs to do more than one of their own chores at the same time. As we'll see in the next two articles, multithreading can lead to significant performance gains, but at the same time make programming a more complex challenge for you.

Until recently, multiprocessor systems were designed by putting two or more discrete CPUs on a motherboard, and were generally limited to high-end servers and graphics workstations. Recently, AMD has introduced CPUs that include multiple processors, or cores, on a single chip. These designs are rapidly entering the mainstream, and are available on servers, desktops, and laptops today. Multi-core CPUs open the door to many possibilities but also pose unique programming challenges. We'll look at these possibilities and challenges in the next article.

© Copyright 2006 Jupitermedia Corporation. All Rights Reserved.

# Multiple Threads, Multiple Cores, Multiple Gains: Part 2

Learn how to use multiple cores for faster performance.

### Peter Aitken

In the first article of this three-part series, we saw how modern operating systems, such as Windows, can rapidly switch a single CPU between different tasks such as printing a document, downloading a file, and performing mathematical calculations. Because this happens so quickly, the perception is that these tasks are happening simultaneously. We also saw how a program can be written to use more than one thread, so that a time-consuming task would not freeze the program's user interface. These techniques, multitasking and multi-threading, are today fundamental to the ways that we use our computers.

The fact is, however, that with the vast majority of systems, there is still only a single CPU doing all the work. How can we speed things up? The obvious route to better performance is to design computers with multiple CPUs—after all, it is a lot easier to add a second CPU to a computer than it is to make one CPU twice as fast!

### **Multi-CPU Computers**

Systems with two or more CPUs are not new at all, and some approaches date as far back as the early mainframe days. In today's specialized world of supercomputers, designers have been linking larger and larger numbers of ordinary processors together to generate truly awesome computing speed.

For example, in 2005, IBM's Blue Gene/L used its 65,536 processors to break the existing speed record with an astounding 135.5 TFLOPS (FLOPS, or floating point operation per second, is a standard measure of computing speed, and a TFLOP, or TeraFLOP, is a trillion FLOPS—or  $10^{12}$  FLOPS). More recently, the Lawrence Livermore National Laboratory announced that its 131,072-processor machine has reached 207 TFLOPS. In contrast, a fast personal computer might reach 10 GigaFLOPS (GFLOP =  $10^9$ ).

These supercomputers are all specialized for computation-intensive tasks such as weather forecasting, modeling nuclear weapons, and molecular simulations. Such models work in multiprocessor computers only because their tasks can be broken into many separate subtasks that can be performed in parallel. This, in turn, is possible only when each subtask does not depend, or depends very little, on the results of other subtasks in the model. For example, in weather forecasting, a large area can be conceptually divided into thousands of smaller square areas, and the weather calculations for each area can be assigned to one processor.

In the less exotic world of personal computers, two- and four-CPU systems, with each CPU on a discrete chip, have been around for a while. This technology is known as *symmetrical multi-processing*, or SMP, because all of the processors are identical to each other. These systems tended to be expensive and have been used primarily as servers and high-end graphics workstations, where the added throughput justified the extra cost.

The fact is, however, that most programs cannot currently benefit from multiple processors. You will remember from the first article that the operating system assigns CPU time to program threads, but most programs have only the single, default thread. The system could have a dozen

CPUs, and a single-threaded program would still not take advantage of them. There are exceptions, however. One example is Adobe Photoshop, which has supported multi-threading for quite awhile now and can take advantage of multiple processors when they are present.

Multi-CPU systems can offer benefits to the end user, even when he or she is not using multithreaded apps. It's a rare system that does not have multiple things going on at the same time, even when only a single application program is running. A slew of background processes is often at work performing tasks such as system maintenance, virus scanning, and file indexing. When two or more CPUs are available, these tasks can run faster and more efficiently by being assigned to different threads—and therefore to different CPUs—by the operating system.

### **Multi-Core CPUs**

As integrated circuit manufacturing techniques have improved, several factors have combined to motivate the development of multi-core chips that contain more than one CPU. Some of the more important factors were:

- It has become becoming increasingly difficult to increase performance by upping the processor clock speed.

- The use of existing, proven core designs in new configurations decreases development time, cost, and both financial and technical risk.

- Multi-core chips lower manufacturing costs. That is true for both the chips themselves, because it is cheaper to manufacture one *n*-core chip than *n* single core chips, and for the motherboards, because a multi-core chip requires less motherboard real estate, only one socket, and fewer interconnections.

On a more technical level, multi-core designs offered additional advantages over implementing SMP with multiple discrete processors. One advantage has to do with the cache coherency circuitry. Each CPU has a local cache of extremely fast memory where it keeps a copy of data from the system's main RAM. With multiple processors, it is possible for one processor to change the data in RAM, leaving another processor's cache with outdated data. Cache coherency circuitry monitors changes to RAM data and ensures that all processor caches have the most recent data. When processors, or cores, are on the same physical chip, the cache coherency circuitry can operate at the very high speeds of on-chip communication, rather than having to use the much slower between-chip communication, as is required with discrete processors on separate chips.

Another advantage of multi-core chips is related to power consumption. An *n*-core processor requires less power than the equivalent number of discrete single-core CPUs, partly because on a multi-core chip, the cores can share some circuitry, such as the HyperTransport interface, that must be duplicated on each single-core CPU, and partly because there is less external support circuitry required on the motherboard. Less power consumption means less heat to dissipate, longer laptop battery life, and lower energy costs.

From the outset of AMD's 64-bit processor strategy, its architecture was designed to accommodate multi-cores on a single chip. Currently, AMD is producing dual-core processors for desktops, notebooks, and servers. Quad-core processors are slated for availability next year.

### **Software Design Considerations**

For the vast majority of end users, working with a multi-core system is totally transparent. Some

programs may run faster, and background tasks will complete more quickly, but otherwise, you can just go about your work as you always have. For software developers, however, things are not quite so simple, because, just as with any SMP system, making the best use of the power of SMP can pose some thorny challenges.

Some challenges arise at the conceptual or design level. If a programmer wants to use multithreading on a multi-processor system to truly increase performance, it is necessary to break a time-consuming task into two or more parts that can each be assigned to its own thread. Because these threads will be executing at the same time, each on its own processor, they need to be largely independent of each other, although not necessarily completely independent. Simply put, Thread A cannot be dependent on the results of Thread B to carry out its actions, and *vice versa*.

Some computing tasks are inherently linear in nature and will resist all attempts to divide them up for faster processing with multiple threads. Other tasks require a great deal of creative thought and experimentation before they can be successfully broken down for parallel processing. Other potential problems with multi-threading exist at the level of source code—or, as is often said, the devil is in the details.

One such problem is the so-called *race condition*, in which the outcome of the overall process is dependent on the order in which the individual parts, or threads, complete. Race conditions can occur when two or more threads access and change the same data, as often happens when multiple threads are not totally independent of each other.

For example, suppose that at some point during its execution Thread A changes the variable X, and at some point during its execution Thread B reads the variable X. The overall outcome will differ depending on whether Thread B reads variable X before or after Thread A changes it. Programmers must use various thread synchronization techniques to prevent such race conditions from invalidating their program's results.

A related potential problem is a *deadlock*. It occurs when two or more threads are each waiting for the other to finish something, with the result that all threads are frozen. As an example, consider an application that uses multiple threads to perform complex operations on a database. To avoid race conditions, each thread puts a lock on each individual table that it accesses and releases the lock when finished. Then the following could occur:

- 1. Thread A puts a lock on Table X.

- 2. Thread B puts a lock on Table Y.

- 3. Thread A now needs to access Table Y but cannot get it because that table is locked by Thread B (which is waiting). Hence, Thread A waits and never releases Table X which prevents Thread B from continuing

- 4. Thread B now needs to access Table X but cannot get it because that table is locked by Thread A (which is waiting). Hence, Thread B waits and never releases Table Y which prevents Thread A from continuing.

Avoiding deadlocks and race conditions is a difficult programming task, and a well-designed multi-threaded program will include not only the logic to prevent them but also code to resolve them when and if they do occur—something that not even the best programmer can always prevent.

### **Multi-Threading Today**

Despite the difficulties that are inherent in writing multi-threaded programs, numerous companies have surmounted these challenges. In the third article in this series, we'll take a look at Modo, a state-of-the-art three-dimensional design and modeling package from Luxology that was written to take full advantage of modern multiprocessor systems. We'll also discuss how careful architecture of a program's design can optimize performance on a multi-core or other SMP system, and why careless architecture can lead to disastrous results.

© Copyright 2006 Jupitermedia Corporation. All Rights Reserved.

# A Quick Look at the Benefits of Multi-Core Computing

Learn how AMD Direct Connect Architecture and AMD HyperTransport technology can help you improve your multi-tasking.

### by Tyler Anderson

Have you ever tried to run multiple tasks on your current computer? Some days it slows to a crawl like it's trying to wait until it has dried out under the sun. And think of those excruciating freezes that can happen when you try to run the CD/DVD drive and an application at the same time.

That's where multi-core systems can help. The term sounds pretty cool—multi-core—but what does it mean? It means multiple processors combined onto a single silicon chip. This is not a small undertaking, and it involves engineering ingenuity. However the payoffs are great, with tremendous value for the home and business user.

I recall the first time that I ever used a multi-processor system. It was back in my days as a Research Assistant in an impoverished research lab at the university I attended. The reason I say impoverished is because the computer was a Pentium III (in a time when AMD had already released their dual-core Opteron and Athlon 64 processors and Intel had released Hyper-Threading). However, this was not just any Pentium III computer; it had two processors on it—the latest and greatest setup of its time (a decade ago)! Booting up and initial loading of your favorite and essential apps on even today's modern processors can be slow, but on this computer I could load several apps, yet I was always able to simultaneously play with the mouse cursor while I waited for Mozilla to load in the background. I don't know about you, but I was impressed. Being able to play with the mouse while waiting, or be able to comfortably compile source code and run compute-intensive applications at the same time? Now that's true multi-tasking.

There's a name for this—Multi-Processing (MP), which distributes loads across multiple processors in a single system. MP allows you to do more than play with a mouse—potentially a home user could burn a DVD or CD at the same time they are downloading music from the Internet. Though technically you can do those things on a single-processor system now thanks to time-sharing, the problem is that a single CPU can easily be overloaded. A user burning a DVD is likely to just create a coaster if there aren't enough CPU cycles available to meet the demand. Having more than one CPU makes this sort of multi-tasking much easier. In business and science, MP is a way to support multiple users and their applications on a single system. In the past, MP has most commonly been seen in very high-end home desktops, business and scientific workstations, and servers.

For the home user, multi-core means they'll now get the power of a workstation on their desktop, and they'll be able to do a lot more in terms of running more applications at the same time. So what does it mean for developers? More than you might expect.

### The AMD64 Design

Why multi-core? Power consumption, heat, and their effects on clock speeds are a major factor in pushing the industry towards multi-core technology. At the current state of the art with AMD's manufacturing process, it's been found that going back two 200 MHz steps from the maximum clock frequency decreases power consumption by 40%. In other words, at high frequencies, the power consumption increases disproportionably as the clock frequency goes up. The most

important factor affecting power is the number of transistors, and that's affected by the microarchitecture and the size of on-chip cache (typically the L1 and L2 caches). All this adds up to current leakage and thermal issues that snowball with greater clock frequencies. Bottom line is that the clock cycle increases we've seen in the past can't be sustained, and that leads us to multi-core.

The trouble with adding all this extra computing power of multi-core is the load it will place on the system. Imagine a 4-way (aka 4-socket) system with dual-core CPUs; that's a total of 8 cores. In the past, most MP systems have traditionally been Symmetric Multi-Processing, in which multiple CPUs share a single main memory. With traditional SMP, it's too easy to stall the system by consuming all the memory bandwidth. If it's possible to overload a 4-way single-core SMP system, then 8 cores is going to just make things worse.

AMD planned for multi-core when it designed AMD64. The most obvious facts of AMD64 are 64bit addressability and 16 64-bit registers instead of 8 32-bit registers. But there's a lot more to AMD64 besides that. AMD recognized the scalability problems inherent in traditional SMP designs, which is why you don't often see commodity servers with more than four processors (unless they're AMD64). CPUs on SMP can easily be starved because of the lack of memory bandwidth. Another subtle but real problem is cache coherency—correct functionality requires that CPU caches mirror each other if they address the same data; the synchronization overhead for this can bottleneck a system, severely impairing scalability. AMD improves scalability tremendously with the Direct Connect Architecture that allows for great scalability with multi-core. DCA is a smart alternative to traditional SMP.

### Scalability and the Direct Connect Architecture

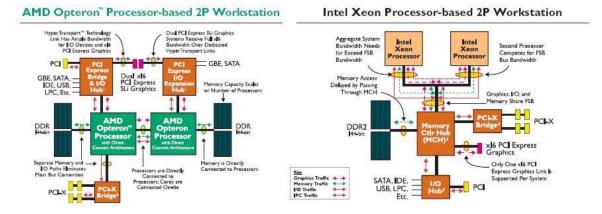

**Figure 1.** Key differences in the architecture connecting the AMD Opteron processor vs. the Intel Xeon.

One of the most important aspects of the AMD64 design is AMD's Direct Connect Architecture. Traditional SMP systems are bottlenecked by the Front Side Bus and memory controller hub, inhibiting top multi-core performance and capabilities. Picture the nasty highways on your way to work. In the single core architecture, we have two points, memory and other I/O at your place of residence, and the processor sitting where you work with a long, two lane highway connecting them. The traffic along the highway, instead of vehicles, is packets of data to and from memory

and I/O. Traffic can't get too bogged down since there is only one exit on each highway-at the end. Now imagine not one, but two processors side by side on the one side of the school using the same highway. What do you think will happen? Optimally, both processors won't be trying to send requests to memory at the same time or the highway will get more and more congested. Not only does a processor have to wait for data to come back from memory, but a processor also has to take turns sharing the highway with the other processor. Figure 1 shows key differences in the architecture connecting the AMD Opteron versus the Intel Xeon.

In AMD's Direct Connect Architecture, each multi-core chip gets its own memory controller, reducing the bottleneck point on traditional multi-core systems at the Northbridge where each processor would have to fight for a chance at memory. The old two-CPU Pentium III I used to work on suffered from this problem, too. Even though there were two processors in the computer, the maximum memory bandwidth didn't change, causing overall throughput to not increase as much as one would like or hope. Good thing the memory requirements for playing with the mouse pointer aren't too high.

With AMD's Direct Connect Architecture, the memory bottleneck problem is alleviated, since the DCA design is also a Non-Uniform Memory Architecture (NUMA) design for systems with two or more processors. In the scenario of two dual-core AMD64 processors, instead of one highway connecting both dual-core CPUs to memory, each CPU gets its own highway—*and* separate highways to both memory (via an integrated memory controller) and I/O. In a nutshell, AMD's Direct Connect Architecture connects processors directly to each other, memory, and I/O. This greatly reduces the bottleneck, resulting in increased performance.

AMD's HyperTransport Technology is the booster that adds speed to the highways in the Direct Connect Architecture. Thus, instead of sluggish traffic-prone highways, something more like speedways (or several-lane highways) exists, three of them in fact, apart from the integrated memory controller. Each of the three links are known as HyperTransport links with up to 8 GBs worth of bandwidth per CPU with the memory controller providing up to an additional 6.4 GBs, allowing a top speed of roughly 30 GBs. Take a look at Figure 2 for comparison data with AMD Opteron versus Intel Xeon, Pentium 4, and Apple's G5.

| Workstation System Comparison             | AMD Opteron"                 | Intel Xeon            | Intel Xeon <sup>1</sup> | Intel Pentium® 4      | Apple G5'           |

|-------------------------------------------|------------------------------|-----------------------|-------------------------|-----------------------|---------------------|

| Modular, glueless scalability             | Yes                          | Requires Northbridge  | Requires Northbridge    | Requires Northbridge  | Requires Northbridg |

| SMP Capabilities                          | Up to 8-way                  | Up to 2-way           | Up to 2-way             | I-way                 | Up to 2-way         |

| Direct Connect Architecture               | Yes                          | No                    | No                      | No                    | No                  |

| Dual-Core technology                      | Yes                          | No                    | No                      | No                    | No                  |

| High Performance 32-bit and 64-bit comput | ting AMD64                   | EM64T                 | EM64T                   | EM64T                 | Yes                 |

| HyperTransport™ technology                | Yes                          | No                    | No                      | No                    | Yes                 |

| Integrated DDR memory controller          | Yes                          | No                    | No                      | No                    | No                  |

| Front Side Bus frequency                  | 1.4 – 2.6GHz†                | 533MHz                | 800MHz                  | 800MHz                | 900MHz - 1.25GHz    |

| Front Side Bus bandwidth                  | 11.2 - 20.8GB/s <sup>†</sup> | 4.3GB/s               | 6.4GB/s                 | 6.4GB/s               | 7.2 - 10GB/s        |

| Maximum Inter-processor bandwidth         | 8.0GB/s                      | 4.3GB/s               | 6.4GB/s                 | N/A                   | 7.2 - 10GB/s        |

| Memory support                            | DDR200/266/333/400           | DDR266                | DDR333/DDR2-400         | DDR2-400/533          | DDR333/400          |

| Memory Bandwidth IP System                | 6.4GB/s                      | 4.3GB/s               | 6.4GB/s                 | 8.5GB/s               | 6.4GB/s             |

| Memory Bandwidth 2P System                | 12.8GB/s <sup>ttt</sup>      | 4.3GB/s               | 6.4GB/s                 | N/A                   | 6.4GB/s             |

| Memory Bandwidth 4P System                | 25.6GB/s <sup>##</sup>       | N/A                   | N/A                     | N/A                   | N/A                 |

| Maximum Graphics Support                  | xI6 PCI-E (xI6 SLi)          | 8X AGP                | ×16 PCI-E (×8 SLi)      | xl6 PCI-E (x8 SLi)    | 8X AGP              |

| LI cache size (max.)                      | 64KB (Data) + 64KB           | 8KB (Data) +          | I6KB (Data) +           | I6KB (Data) +         | 32KB (Data) +       |

|                                           | (Instruction) per core       | I2k mop (Instruction) | I2k mop (Instruction)   | 12k mop (Instruction) | 64KB (Instruction)  |

| L2 cache size (max.)                      | IMB per core                 | 5I2KB                 | 2MB                     | 2MB                   | 5I2KB               |

| L3 cache size (max.)                      | N/A                          | 2MB                   | N/A                     | N/A                   | N/A                 |

| Maximum I/O bandwidth IP System           | 8.0GB/s <sup>#</sup>         | 3.2GB/s               | 4.3GB/s                 | 2GB/s                 | 4.3GB/s             |

| Maximum I/O bandwidth 2P System           | 24.0GB/s##                   | 3.2GB/s               | 4.3GB/s                 | N/A                   | 4.3GB/s             |

| Maximum I/O bandwidth 4P System           | 32.0GB/s <sup>†††</sup>      | N/A                   | N/A                     | N/A                   | N/A                 |

| SIMD Instruction Set Support              | SSE, SSE2, SSE3              | SSE, SSE2             | SSE, SSE2, SSE3         | SSE, SSE2, SSE3       | AltiVec             |

**Figure 2.** Comparison data for an AMD Opteron processor-based workstation vs. Intel Xeon, Pentium 4, and Apple G5.

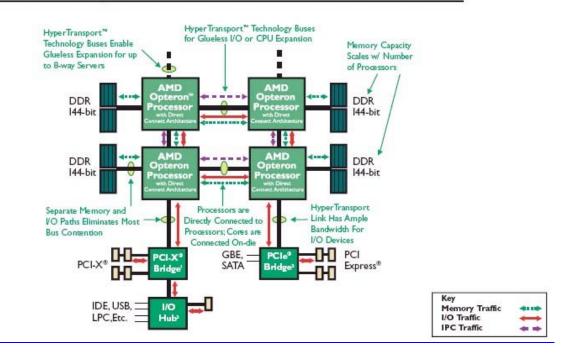

Can you see the scalability advantages as well? Adding a third CPU to the setup doesn't increase the load on the memory controllers of the first two CPUs, since each CPU gets its own integrated memory controller, its own connections to one or two neighboring CPUs, and I/O. With four CPUs in the mix, the four CPUs are positioned in a square. You can compare an Intel 2-socket system versus the AMD 2-socket system back in Figure 1. The 4-socket AMD system is shown in Figure 3. Positioned in this fashion, each processor can be connected to both of its closest neighboring CPUs via two HyperTransport links, memory via the memory controller, and/or I/O via the third HyperTransport link. The performance of each single CPU is no longer dependent on the other CPUs, thanks to the Direct Connect Architecture and HyperTransport Technology. We actually aren't limited to four CPUs; Direct Connect Architecture is designed for 8 CPUs, which means you can get an 8-way Opteron system as a highly scalable off-the-shelf, commodity-priced yet enterprise- capable server.

# AMD Opteron<sup>™</sup> Processor-based 4P Server

Figure 3. Diagram of an AMD Opteron processor-based 4P Server

Also remember the issue of cache coherency; with Direct Connect Architecture, the point-to-point HyperTransport links allow very fast cache synchronization. However on a traditional SMP system, cache synchronization is bottlenecked by the Front Side Bus and the memory controller hub.

### **Multi-Threading Concerns**

Are we faster yet with multi-core? Maybe not. It's critical to understand whether applications are multi-threaded. If your application is not multi-threaded, it will not show any performance improvement with multi-core, other than the side effects you get from background processing such as downloading file, printing, or virus scans.

To really take advantage of multi-core, you need multi-threading. Because of all the previous history with SMP, there's already a lot of software out there that does this. With data parallel threading, units of data can be independently processed by the same piece of code, and this can be seen in applications such as digital signal processing and simulations. Another type of threading is task parallel threading which is different complex functions running asynchronously on different tasks; an example would be a web server handling JSP and CGI services.

Multi-threading smart with multi-core may take some thinking. Suppose for example that you have a number-crunching scientific application that uses data parallel threading and by default grabs every CPU when it multi-threads. Let's suppose it scales very well and it runs a job in 1/6th the time on 8 single-core CPUs versus one single-core CPU (scaling better than that is really hard to do). So it takes an hour with 1 CPU and 10 minutes with 8 CPUs. Throw dual-core into the mix,

giving 16 cores total. At best it may run in 5 minutes, though in reality it would probably be a little longer than that. The law of diminishing returns means that you may not care much whether it takes 5 or 10 minutes. Certainly, either one is much better than an hour. If the application had a tuning knob to allow it to just take 8 cores for the job, then that means there will be 8 cores available for other tasks or other users. To make this happen though, developers need to learn how to query the number of cores and provide tuning knobs for their users. OS vendors such as Microsoft are providing APIs for this purpose.

AMD is preparing for the future by laying the groundwork with the Direct Connect Architecture and HyperTransport Technology found in AMD64 single- and multi-core processors. Now that the technology is developed and proven in silicon-and as the demand for more memory bandwidth and more processors per system grows-AMD is already ahead of the game. Home users will get more power to let them do more than ever before. Developers that are interested in multithreading need to find out about APIs for querying the core count in their favorite operating system. They also need to learn about data parallel versus task parallel threading techniques. Rest assured that AMD will continue to leap ahead of the competition in architectural strides, building upon this framework of technologies, with further revs of their processor lineups.

© Copyright 2006 Jupitermedia Corporation. All Rights Reserved.

### To Thread, or Not to Thread, in a Virtualized World

Learn how threading and virtualization can work together to make your application fly.

### Steve Apiki

It used to be, as application designers, we could follow processor news from a distance. Whatever changed underneath, our program's performance could always hitch a ride on increasing clock frequencies, or on the work of compiler writers and systems programmers. But multi-core processors like the Dual-Core AMD Opteron have changed the game, requiring that application designers more directly participate in the process. The only way to make the most of a Dual-Core AMD Opteron, or any future multi-core processor, is going to be to build in concurrency at the application level.

The latest processor news is all about virtualization. AMD-V virtualization technology, due later this year in the Opteron and Athlon 64 lines, delivers hardware support to virtual machine managers. The industry's shift to virtual machines, while maybe not as profound to application programmers as the dawn of multi-core, also bears watching because it changes the execution environment of our software.

How do these two factors, together, change the way we approach application design? At a high level, multi-core and virtualization seem to play against one another. That is, application designers could rewrite to support parallel execution on several cores, or they could, instead, anticipate programs that run isolated on a single virtual core, no matter what the underlying hardware. In the second case, the effort to carefully decompose the application into component threads might go largely unrewarded.

For many domains, especially on the client, finding tasks that can be handled in parallel isn't easy. And even when sections of code ripe for threading are obvious, implementing threads with today's tools is tough. Debugging is a third challenge. In short, building a heavily-threaded application is generally a more expensive proposition than building one that is single-threaded. So while multi-threaded applications are necessary to take full advantage of multi-core processors, there is a cost associated with the process. Not every application is going to justify that cost.

### Virtualization on the Server: Scaling Out

Virtualization is about isolation—isolation so that different operating systems and their associated binaries can share the same hardware, isolation so that development builds can be tested safely, isolation for secure execution of untrusted code—but it is as also about effective resource utilization. Virtualization makes it possible to flexibly define sets of resources. For example, memory can be parceled out to different processes in different virtual machines, even overcommitted, and the allocations between these machines modified to adapt to changing loads or requirements.

Cores can be allocated to virtual machines in much the same way, at least under hypervisors that support SMP. These include VMware with Virtual SMP, and Xen as of version 3.0. Microsoft has also talked about supporting SMP in future releases. In these environments, multiple cores (or processors) can be assigned to single virtual machines. Hypervisor SMP support takes away the disincentive to thread applications that will likely run on virtual servers, because even here, different threads from the same application can be scheduled on different physical cores.

So, virtualization doesn't restrict you from gaining performance by threading applications on multicore processors. But it does point toward another path to concurrency: scaling out with virtual clusters. Clusters are interesting in this context not so much because they are any easier to implement than threads, which they aren't, but because once built on a set of virtual nodes, the same design can be scaled literally outside of the box to a number of real nodes. A dual-core system running a set of virtual machines makes an attractive development and initial deployment cluster.

### **Concurrency Continuum**

Clustering occupies the end of the concurrency scale that's farthest away from threads, but it is still concurrency, and concurrency is what is required to take full advantage of multi-core. Somewhere in the middle is the notion of partitioning an application by process, at a higher level than threads, but without the isolation and overhead of virtualization.

Having a Web-facing server communicating with a database back end isn't quite partitioning by process in the sense that we're discussing here. In this common arrangement, concurrency is actually achieved by threading within each process. The idea of process-level concurrency is to write single-threaded processes that can run in parallel, communicating with one another at the process level.

Processes are heavier than threads, of course, and with that weight comes advantages and disadvantages. The biggest advantage is that processes don't share memory, so the very real difficulties of managing shared memory access with locks and related synchronization objects disappear. The biggest disadvantage is that multiple processes don't share memory, so any kind of low-level cooperation involving shared data is out of the question.

On the server, the requirement to smoothly provide services to more than one client almost certainly makes concurrency already a design goal. Multi-core doesn't change that. Although threading is the prevailing mode, it may be helpful to keep in mind that there is a continuum of concurrency options, ranging from lightweight threads running in a shared memory space to a clustered server partitioned into heavyweight virtual machines.

AMD's dual-core design makes the Opteron well suited for any of these concurrency choices. I've been using the terms "core" and "processor" almost interchangeably, but dual-core doesn't quite equal dual-processor. A Dual-Core AMD Opteron shares a single memory controller and set of HyperTransport interfaces in common between its two cores. That limits each core's access to memory and I/O relative to a dual-processor Opteron system. Fortunately, the sharing of these resources is handled by an efficient crossbar switch, minimizing any performance loss. This architecture, along with hardware virtualization support, will make the Dual-Core AMD Opteron an excellent virtual machine platform.

On the other hand, multi-threaded designs might additionally exploit the dual-core Opteron's superbly efficient handling of shared memory. On a dual-core processor, threads from a single process can be scheduled on the same chip, on different cores. Shared data structures are likely in both L2 caches, and the Opteron manages cache coherency. Updates from one L2 cache to the other to ensure cache coherency run on-chip, through the system request interface. That means your multi-threaded application gets the benefit of running on multiple physical cores with trips to main memory kept to an absolute minimum.

Threading may be used in network servers as a means of dealing with I/O requests. An alternative network server technique, called select-based, uses just a single thread to multiplex network traffic. Select-based concurrency uses an operating system select() (or a related system call, depending on the specifics of the design) to monitor activity on a set of non-blocking sockets. This approach has proven to scale effectively, but multi-core might start to tip the balance back toward a multithreaded/blocking socket approach.

### Threads on the Client

On the server, your choice between threading and not threading revolves around choosing alternative methods of providing concurrency. It's a different matter on the client, where concurrency is optional, but threading is the only practical concurrency technique. On the client, the question is simpler: is it worth the cost to thread this application, or not?

If you don't thread, your application may still see some benefit from dual-core, in the form of another core on which to run other applications, OS services, and background processes, such as anti-virus software. That may well be good enough for now. But the user's perception of "good enough" will change if other desktop software becomes aggressively multithreaded, and could change even further if a four-core Athlon 64 should materialize.

Virtualization doesn't change the client picture much, because it's unlikely that virtualization on the client will become so dominant a model that we could afford to ignore clients running on bare multi-core machines.

So unless you can accept a performance plateau in the near future, you will need to thread thick client applications. The short-term goal should be to identify the most obvious segments of your application that can benefit from concurrency, and to go after this low-hanging fruit.

On this list would be tasks long associated with parallel processing, such as rendering, speech recognition, and other media-related tasks. In some cases, these may already be handled by threaded code.

Actually implementing threads is by no means easy. Minimizing critical sections to keep threads running as freely as possible, avoiding deadlocks, and debugging subtle race conditions all come with the territory.

But it's after those obviously threadable sections have been built that we come to the really hard part, and that is factoring a generic desktop application into multiple threads. This is the stickiest part of the threading problem, and it's where we find ourselves right now, or will at the next design cycle. We're used to factoring designs along other axes: into classes, into modules, into model, view and controller. We're going to need to develop the skills to see opportunities for parallelization just as well, if we are to continue to bring client software along the performance curve.

© Copyright 2006 Jupitermedia Corporation. All Rights Reserved.

# Living in a Multi-Core World: Tips for Developers

Learn how to best take advantage of advances in multi-core processing.

#### by Justin Whitney

Multi-core has arrived. While multi-processor configurations have been around for awhile, AMD produced the world's first x86 multi-core processor in late 2005 with its Opteron 64 Dual-Core processor. Built primarily for servers, this paved the way for the Athlon 64 X2 Dual-Core, for desktops and laptops, and the Turion 64 X2 Dual-Core, created primarily for lightweight laptops.

As the first dual-core machines hit the market, consumers begin to discover the joys of serious multi-tasking, like listening to music while downloading a movie (legally), browsing, and running a virus scan, just as an example. But while multi-core processors give consumers major performance gains by virtue of their architecture, most developers still have a ways to go in learning to adapt to, and thrive in, a multi-core world.

### **Multi-Core Evolution**

When AMD first put designs on the drawing board for a new architecture, it started with several parameters:

- Ease migration to multi-core, as well as heavy power consumption, by speccing the processor to existing footprints.

- Loosen bottlenecks inherent in sharing chip components between multiple CPUs.

- Fit well in a virtualized environment.

- Set the foundation for an evolution beyond dual-core, into quad-core and beyond.

To overcome their various hurdles, AMD implemented a number of new features, far too many to list here. But the features that are perhaps most pertinent to developers include:

- Improvements in power consumption

- Individual L2 cache per core

- Memory- and thread-affinity

- Positioning for virtualization

In addition to being familiar with these aspects of 64-bit and multi-core architecture, developers can also benefit from knowing what Microsoft has in store for a multi-core world with the upcoming release of Vista. That's covered here, as well as some specific developer tips for coding to multi-core platforms, both in managed and native code.

### Staying Cool Under Pressure